近些年大家都在热衷造芯片、造处理器,RISC-V是经常能听到的一个词。RISC-V公开的ISA指令集,但是具体如何实现并没有统一的标准,所以网上有很多开源的RISC-V实现。tinyriscv就是开源的版本之一,并且作者编写的文档也很全,非常适合新手用来练手和学习RISC-V。

软硬件说明:

本文记录了佐大在移植tinyriscv过程中遇到的一些问题,希望这篇文章能帮助到大家。佐大用的开发板是Terasic DE1、Digilent Nexys4-DDR,对应软件版本是Quartus II 13.0、Vivado 2018.3。

Vivado:

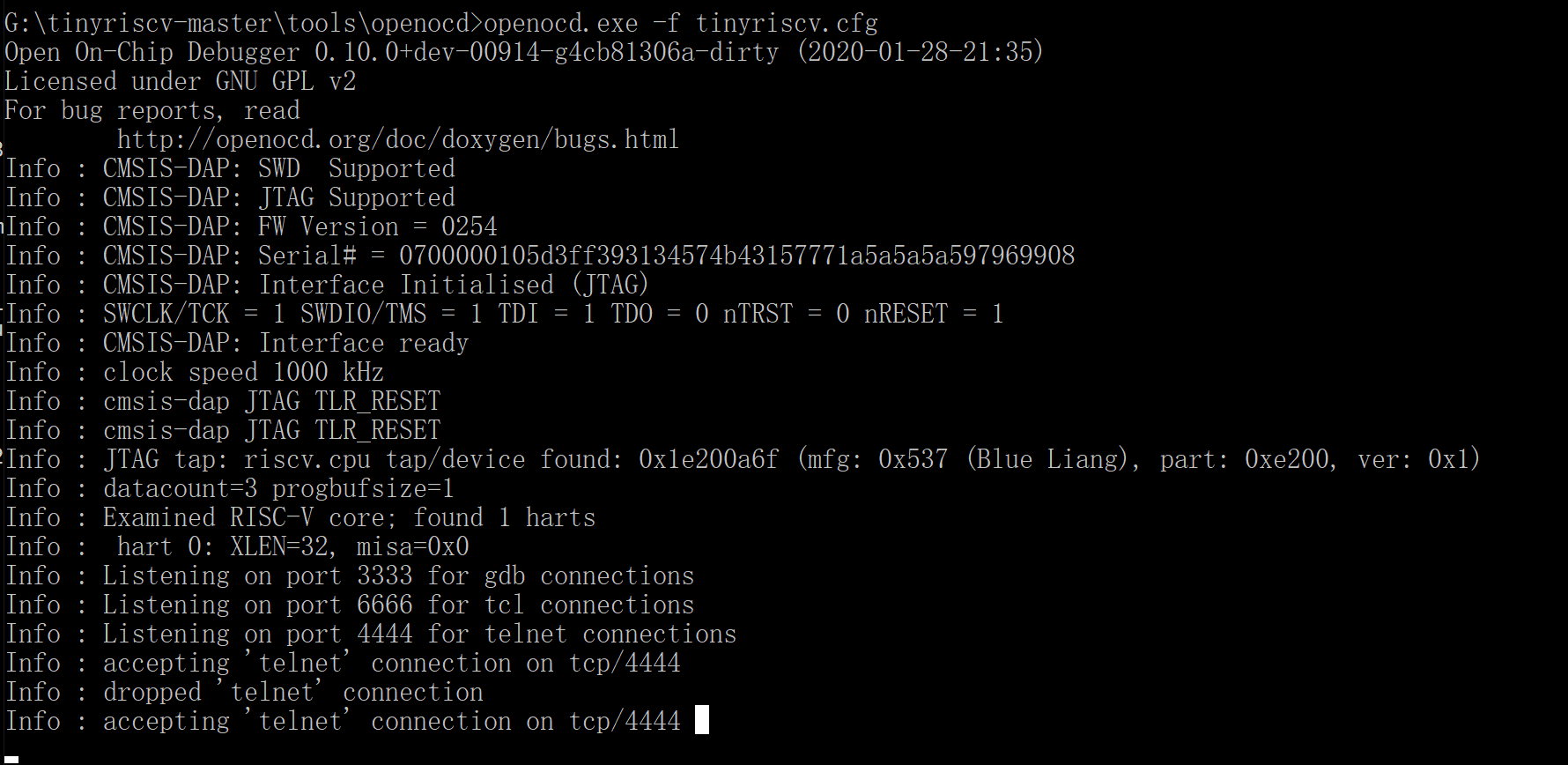

在Vivado平台上,佐大用的是tinyriscv的master分支。由于master分支默认的clk主频是50M HZ,而Nexys4-DDR的clk时钟是100M HZ,所以需使用PLL分频到50M HZ。在约束引脚的时,佐大把UART指到了开发板USB UART的引脚,就在这里踩坑了。使用tinyriscv_fw_downloader.py上传ROM始终失败,折腾半天发现是Nexys4-DDR USB UART兼容性问题,把UART约束到PMOD引脚就正常了。

Quartus:

在Quartus平台上,tinyriscv的master分支有如下问题:1.Quartus不允许申明特别大容量的reg会报错。2.佐大尝试增加bram功能失败了。所以佐大最终用的是tinyriscv的bram分支。由于DE1性能太弱了clk跑不了50M HZ,所以clk用的是24M HZ,同时需修改rtl/core/define.v中的CPU_CLOCK_HZ 为24000000。

在申明RAM IP核时,使用单周期、不锁存q、宽度32bit、深度根据你开发版资源自行设置。然后修改rtl/perips目录的rom.v和ram.v的代码即可,下面是佐大的参考代码。

/* gen_ram #( .DP(DP), .DW(32), .MW(4), .AW(32) ) u_gen_ram( .clk(clk), .addr_i(addr), .data_i(data_i), .sel_i(sel_i), .we_i(we_i), .data_o(data_o) ); */ ip_rom u( .clock(clk), .wren(we_i), .byteena(sel_i), .address(addr), .data(data_i), .q(data_o), );

由于作者使用的Vivado平台,并没有考虑到Quartus的兼容性问题,需要修改rtl\utils\vld_rdy.v文件,下面是佐大的参考代码。

/* if (CUT_READY == 1) begin // If cut ready, then only accept when stage is not full assign rdy_o = (~vld_r); end else begin // If not cut ready, then can accept when stage is not full or it is popping assign rdy_o = (~vld_r) | vld_clr; end */ assign rdy_o = (CUT_READY == 1) ? (~vld_r) : (~vld_r) | vld_clr;

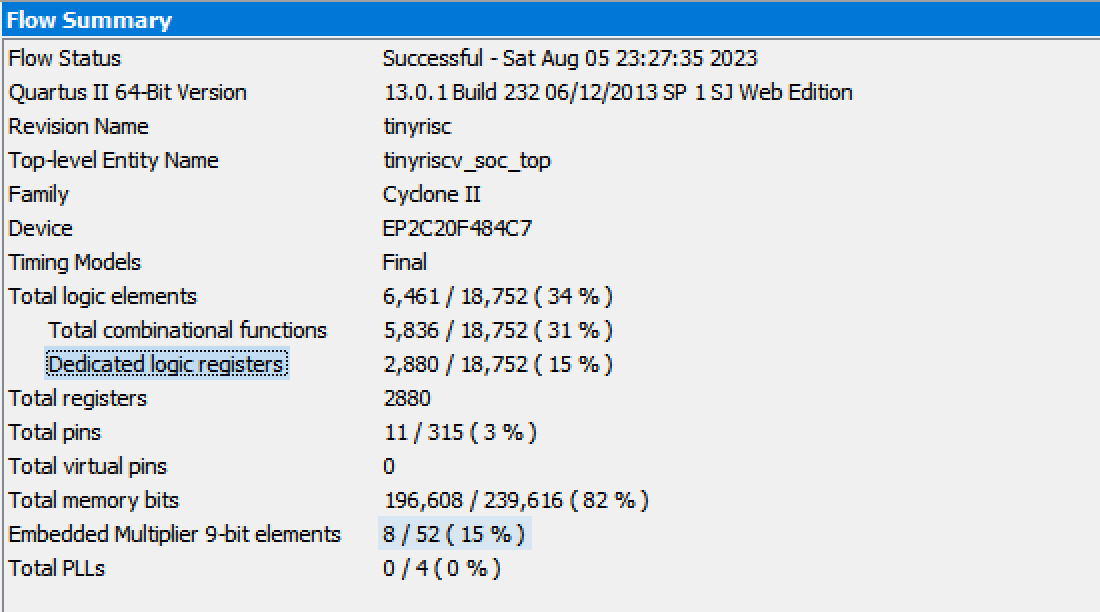

资源占用情况如下图

总结:

本文就是一篇随笔,技术含量不高,更多的是记录佐大最近的动态。参加了佐大OpenWrt培训班的学员,佐大可提供移植tinyrisc的技术指导,希望佐大的绵薄之力能帮助你们成长。